# AN10912 SMPS EMC and layout guidlines Rev. 1 — 18 February 2011

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | EMC, EMI, IEC61000, AC/DC, DC/DC, SMPS, conducted emission, PCB.                                                                                                                                                                                  |

| Abstract | This application note is a guide to assist in the design and layout of a Switch Mode Power Supply (SMPS) Printed-Circuit Board (PCB) as used in adaptors and lighting applications. The SMPS is designed to be compatible with EMC/EMI standards. |

#### **SMPS EMC** and layout guidlines

#### **Revision history**

| Rev | Date     | Description |

|-----|----------|-------------|

| v.1 | 20110218 | first issue |

#### **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

SMPS EMC and layout guidlines

#### 1. Introduction

SMPS converters operate on frequency bands where passive components (PCB, decoupling capacitors, PCB connections, packages) are not considered ideal because they contain parasitic elements e.g. inductance, resistance, etc. Because the impedances are frequency dependant, the emission levels generated by voltage, and current drops may not be compliant with certain EMC standards. Many different EMC standards are used throughout the world. In addition to the localized region or country standards applicable where the design will be utilized, the type of application might also require a specific set of standards to be met in order to pass EMC/EMI standards.

These standards are under copyright and must therefore be purchased through official sales channels.

For the USA market, FCC Part 15 covers radio frequency devices capable of emitting RF energy in the range of 9 kHz to 200 GHz. Conducted emissions are regulated by the FCC over the frequency range 450 kHz to 30 MHz, and the CISPR 22 conducted emissions limits extend from 150 kHz to 3 MHz. Testing should be carried out according to ANSI C63.4-1992. Part 18 covers industrial, scientific, and medical (ISM) equipment.

For the European market, EMC Directive 89/336/EEC sets out the legal requirements for principally all electric/electronic equipment to be placed or used in the common market and the whole european economic area. International standards concerning EMC are primarily developed by the International Electrotechnical Commission (IEC) and the International Special Committee on Radio Interference (Comite International Special des Perturbations Radioelectriques - CISPR).

For the new extensive series developed by the IEC, see Ref. 1 to Ref. 6.

Due to the fact that many EN standards are based on IEC and/or CISPR standards, international and European EMC standards are generally becoming harmonized. There are also some similarities between international and U.S. standards, although they are not interchangeable.

EMC standards are continuously being developed, revised and updated, and much confusion can arise regarding which standards are applicable to specific applications. It is therefore important to always be aware of the publication status for standards, to be aware if a new standard is to be expected in the near future and subsequently, when an old standard becomes invalid.

The following dates are important:

- Date Of Publication (DOP)

- Date Of Withdrawal (DOW) of a conflicting (earlier) standard

Draft standards are sometimes referred to as 'preliminary', for example prETS or prEN. Temporary EN standards are termed ENV.

Standards can be divided into two categories:

- · Generic standards

- Product standards

If no product standard is applicable, the current generic standard must be followed.

#### **SMPS EMC and layout guidlines**

A product standard covers all the EMC requirements for a certain product type. In some cases, product standards will also cover the electrical safety requirements. A product standard takes precedence over all other standards. Once it is determined that a product is within the scope of an applicable product family standard concerning emissions and/or immunity, then that standard should be followed. For some examples of family standards see Ref. 7 to Ref. 12.

More recent product family standards also tend to appear as complementary emissions and immunity standards, see Ref. 13 and Ref. 14.

For specific types of product family standards transferred into general standards see Ref. 15 to Ref. 18.

There are a limited number of pure product standards that cover all EMC requirements, consequently an appropriate product family standard must be used. An additional complication is that a product can simultaneously belong to different product family standards. For example, most household devices must meet emissions requirements according to Ref. 13, as well as Ref. 15 and Ref. 16 or Ref. 17 and Ref. 18.

It is impossible to accurately predict the EMC compliance of a given system, but by implementing specific rules and design techniques in the design of the application, it is possible to considerably reduce the risks. This application note lists the major points which can help to minimize EMI and improve EMC performance. It also demonstrates how some basic techniques can help to reduce emission levels and harden the electronic system.

#### **SMPS EMC and layout guidlines**

#### 2. Scope

This application note offers guidelines for the design and layout for the Printed-Circuit Board (PCB) of an EMC/EMI standards compatible Switch Mode Power Supply (SMPS). SMPS designs are typically used in power supply and lighting applications.

The document is laid out so that each chapter can be read with a minimum of cross references to other documents or data sheets. This will lead to some repetition as the information within this application note may also be available in other, more dedicated documents. Where possible, typical values are used to improve clarity.

- <u>Section 1</u>: provides a brief description of SMPS converters and introduces some international and european EMC standards

- Section 2: outlines the purpose and format of this application note

- Section 3: explains the topology

- <u>Section 4</u>: provides basic checklists for EMC compliance and necessary relevant processes

- Section 5: provides an extensive description of how to reduce HF signature

- Section 6: is a brief conclusion

- Section 7: offers additional information on capacitor marking and codes etc.

**SMPS EMC and layout guidlines**

#### 3. Topology of the EMC environment

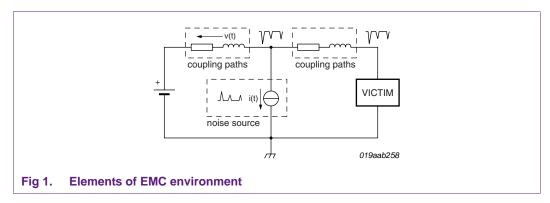

<u>Figure 1</u> shows the topology of an EMC environment. A noise source drives a current  $i_{(t)}$ . This current flows through the left coupling path (a PCB connection for example) and causes a voltage drop. This voltage perturbation is transmitted to the victim through the right coupling path and can cause a malfunction if the level is high enough.

The EMC environment effecting these elements must be analyzed in order to significantly improve the EMC quality of the design.

#### **SMPS EMC and layout guidlines**

#### 4. Basic checklist for EMC compliance

The basic rules for minimizing the conducted and radiated emissions through the power supply, are given in the checklists provided in <u>Section 4.1</u> to <u>Section 4.6</u>.

#### 4.1 Reducing the HF signature of the system

- · Slope and duty-factor control

- Filter and dampen at the noise source

- · Adapt the converter frequency to fit EMC curve

#### 4.2 Reducing the magnetic loops of the PCB

- Decrease the surface area of the magnetic loops

- Use a decoupling capacitor

- Maintain the signal trace close to the return path

- Prevent edge radiation

- Microstrip technology

- Reduce VCC/VSS network

- · Shorten the loops around the oscillator

#### 4.3 Cancelling the H field

- · Opposite magnetic loops

- Complimentary magnetic loops

- Connect V<sub>CC</sub> and ground close together

- Increase the PCB connection widths

#### 4.4 Reducing the parasitics of all devices

- Select the proper PCB technology

- Utilize ground and power planes

- Grounding techniques

- Adapt the decoupling capacitors to the working frequency of the converter

- Shorten the capacitor connection lengths

- Choose COG and NPO dielectric types

- Bypass electrolytic capacitors

- · Adapt inductors to the working frequency of the converter

- Prevent mutual coupling of inductors

- Increase distance between the noise source and the victim

#### **SMPS EMC** and layout guidlines

#### 4.5 Frequency domain analysis

- Differential and common mode noise

- · X and Y type capacitors

- Dampen unwanted HF signals

#### 4.6 Shielding

- Mount hot winding at inner layer

- Attach heatsink to clean potential

- Use component material and heatsink as shield

- Use capacitive shielding

- Decouple other floating potentials

Sub chapters Section 4.1 to Section 4.6 are detailed in Section 5

**SMPS EMC and layout guidlines**

#### 5. Reducing the HF signature of the system

#### 5.1 Slope and duty factor control

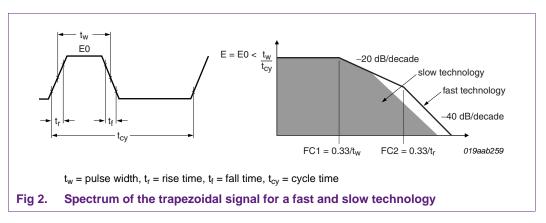

A key element in the reduction of EMI, is the selection of the slowest slope of voltage and current changes in time. This is especially applicable on the main inductors current waveforms and voltages on the switches. The spectral envelope of such a signal, has two cut-off frequencies and is shown in <a href="Figure 2">Figure 2</a>. The first one (FC1), depends on the pulse width of the signal and the second one (FC2), depends on the sharpness of the transition mainly due to the technology used. A more gradual transition and a more even duty-factor, gives a lower EMI signature.

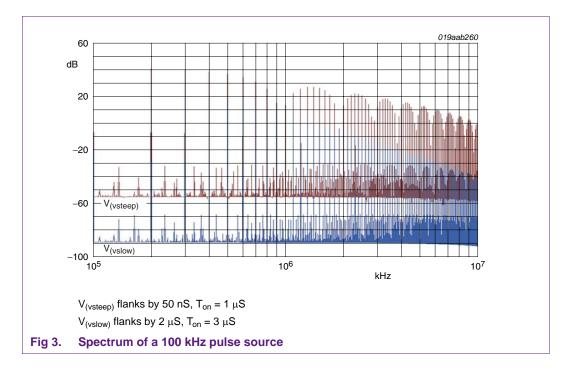

Theoretically, halving the maximum operating frequency limit, reduces the EMI by 12 dB. Figure 3 shows the spectrum of a 100 kHz pulsed source with both steep and slow slopes, and different duty factors.

**SMPS EMC and layout guidlines**

#### 5.2 Filtering and damping at the noise source

One of the basic rules for preventing EMC, is to identify and locate possible noise source(s) and to apply counter-measures to them. They are most common where the largest voltage and current changes occur, e.g. switching elements. Components such as inductors and transformers, can also cause additional noise by oscillating at their resonant frequency when not being driven (ringing). Filtering can block the path from the noise source to the surroundings, but it does not decrease the noise energy. As a result, the signal will look for alternative paths by which it can propagate and damping dissipates the electrical or magnetic energy. A combination of damping and filtering provides the most effective solution.

#### 5.3 Adapting converter frequency to an EMC curve

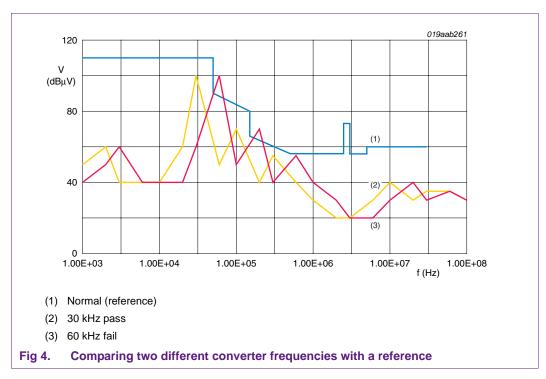

Another key parameter to pass EMI is to adapt the converter frequency to fit with test criteria. Figure 4 shows an example, where a converter at 60 kHz fails and when shifted to 30 kHz passes. The drawback of this method is that lowering the frequency also lowers the power output for a given inductor size. Alternatively, switching losses and filtering may be less. When selecting a converter working frequency, it is beneficial to consider the test requirements.

#### 5.4 Reducing the PCB magnetic loops

#### 5.4.1 Decreasing the surface area of the magnetic loops

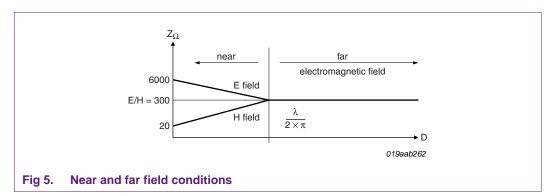

A current flowing around a loop generates a magnetic field (H) proportional to the area of the loop. <u>Equation 1</u> and <u>Equation 2</u> give the mathematical expressions for when the observation distance is in both the near field and the far field conditions.

SMPS EMC and layout guidlines

$$Hnear_{A/m} = I \times \frac{S}{4 \times \pi \times D^3} \tag{1}$$

$$Hfar_{A/m} = \pi \times I \times \frac{S}{\lambda^2 \times D}$$

(2)

where:

- I = loop current (A)

- S = loop surface (m<sup>2</sup>)

- D = observation distance (m)

- $\lambda$  = current wavelength (m)

The near field and far field conditions are expressed by Equation 3:

$$\frac{D}{\lambda} = \frac{1}{2 \times \pi} \tag{3}$$

This ratio indicates the transition at the point where the emission is in far field or in near field condition (see <u>Figure 5</u>). The far field condition is a specific distance where the electrical and magnetic fields are coupled and perpendicular. In this condition, the ratio E/H is the intrinsic impedance of free space equal to 300. In the near field condition the nature of the fields depends on the connection impedance. For a high impedance (Z > 300) the field is electric and for a low impedance (Z < 300) the field is magnetic.

#### Example:

At 3 meters, F = 30 MHz and I = 0.1 A, the magnetic field intensity is  $-19.6~db\mu A$  for a 1 cm² surface loop and  $-13.6~db\mu A$  when the loop surface is doubled. Reducing the surface area by a factor of two will decrease the H field by 6 dB. This can be achieved by carefully checking the PCB layout.

#### 5.4.2 Magnetic loop and ohmic voltage drop

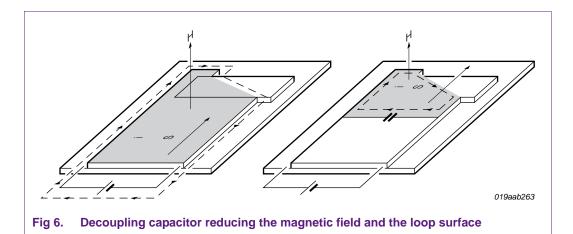

The decoupling capacitor reduces the magnetic loop and ohmic voltage drop. It supplies the fast transient currents locally and reduces the length of the current discharging path. It also contributes to the reduction of the closed contour taken by the current and the radiation surface as shown in <a href="Figure 6">Figure 6</a>. Each fast analog and digital circuit part must be decoupled using a capacitor between power and ground. An additional serial ferrite bead is highly recommended to prevent line voltage oscillations.

#### **SMPS EMC and layout guidlines**

#### 5.4.3 Parasitic inductance

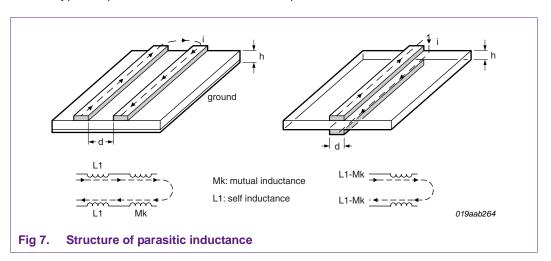

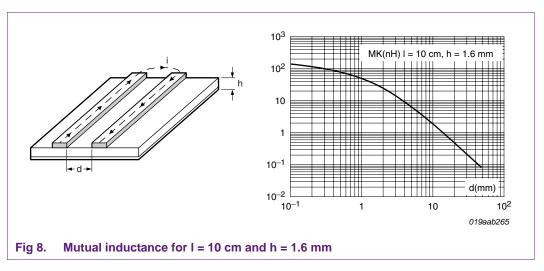

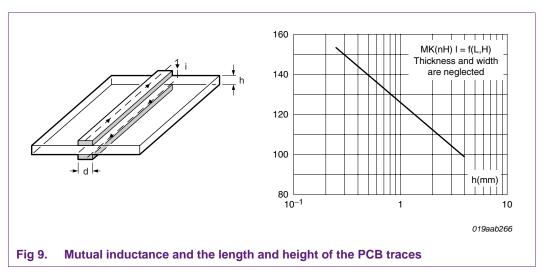

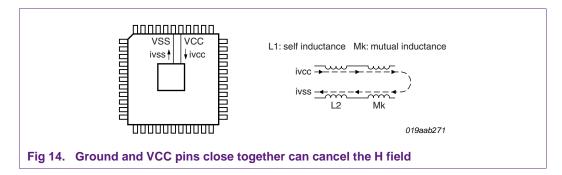

To maintain a low parasitic inductance of a signal trace, the distance to the ground has to be kept short. The parasitic inductance of two parallel conductors carrying uniform current in opposite directions consists of self-inductance and mutual inductance. Figure 7 shows the two types of parallel conductors and their equivalent electrical model.

The total inductance for self-inductance (L1) is given in  $\underline{\text{Equation 4}}$  and for mutual inductance (Mk) in  $\underline{\text{Equation 5}}$ .

$$LT = L1 + L2 - 2 \times Mk \tag{4}$$

$$Mk = k \times L1 \times L2 \tag{5}$$

L1 and L2 are the self-inductance of the individual conductors, and Mk is the mutual inductance between them. If the VCC and VSS are identical, LT is reduced as shown in Equation 6.

$$LT = 2 \times (L1 - Mk) \tag{6}$$

If the coefficient of magnetic coupling (Mk) between the two conductors is unity, the mutual inductance is equal to the self-inductance of one conductor, since Mk = L1 and the total inductance of the closed loop is zero. To minimize the total inductance of the

AN10912

#### **SMPS EMC and layout guidlines**

complete current path, the mutual inductance between the conductors is maximized. Therefore, the two conductors should be placed as close together as possible to minimize the area between them. Figure 8 shows the mutual inductance for different spacing.

Parallel running traces with different signals generally have sufficient distance to prevent crosstalk. These traces should be separated by no less than twice the trace width (2W-rule).

For this configuration, the formula is only applicable if the forward and return currents flow through these two traces. Figure 9 plots different Mk values for various PCB trace dimensions.

<u>Figure 9</u> clearly shows that a smaller height of PCB trace will reduce inductance and therefore also reduce radiation and crosstalk.

#### 5.4.4 Preventing edge radiation

On a PCB with a ground plane, a trace with a high frequency signal running close to the edge of the PCB will act as an antenna. The distance of these traces from the edge of the board should be 20 times the trace height (20 h-rule) i.e. for a PCB thickness of 1 mm, the trace should be 20 mm from the edge.

#### **SMPS EMC and layout guidlines**

#### 5.4.5 Microstrip topology

The total inductance of a loop (LT) is drastically reduced when using a ground plane because the equivalent inductance of the plane ( $L_{Plane}$ ) is much lower than the PCB trace ( $L_{Trace}$ ). This is mainly due to the contour taken by the H-field which is much larger than the contour taken around the signal trace. These two inductances are acceptably independent and so can be evaluated separately. The ground plane inductance is not affected by the PCB trace width and can be calculated using Equation 7.

$$L_{Plane}(nH/cm) = \frac{5 \times h}{W} \tag{7}$$

The PCB trace inductance can be calculated using Equation 8

$$L_{Trace}(nH/cm) = 10^{-9} \times In \left( 1 + \frac{32 \times h^2}{wt^2} \times \left( 1 + \sqrt{\pi \times \frac{wt}{8 \times h}} \right) \right)$$

(8)

This inductance is independent of the PCB ground width. For example a trace of 10 cm length and 1 mm width and separated from the ground plane by 1.6 mm presents an inductance of 51 nH. A plane with the same dimensions and 10 cm width presents an inductance of 0.8 nH. So the total inductance is the sum of the PCB trace and plane (51.8 nH). The same trace without the ground plane has an inductance equal to 115 nH. The trace inductance is reduced by a factor of 2.22 due to the plane.

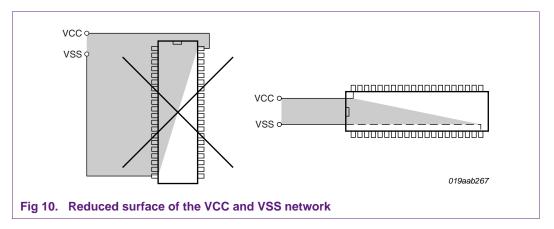

#### 5.4.6 Reducing VCC/VSS network

If there is no dedicated plane for the power, keeping the tracks as close as possible is recommended, in order to reduce the surface of loop and the parasitic inductance that supply power to the IC (see Figure 10).

This method not only reduces emitted fields caused by steep current changes into the IC, but also reduces the susceptibility of the IC to received disturbance.

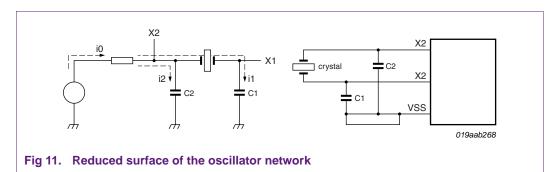

#### 5.4.7 Shortening the loops around the oscillator

<u>Figure 11</u> shows the electrical model of a common oscillator implemented in an IC. At resonance, the fundamental currents i1 and i2 have the same amplitude. In the closed loop mode the oscillator is stabilized in the saturation region of the amplifier that

#### **SMPS EMC and layout guidlines**

generates some harmonics in HF. Consequently, the output loop (X2, C2, and VSS) must be optimized first and then the input loop (X1, C1 and VSS). In both cases they must be as small as possible.

### 5.5 Cancelling the H field

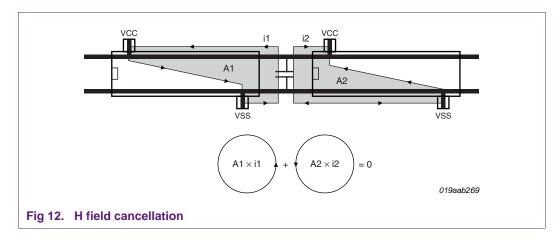

#### 5.5.1 Opposite magnetic loops

Identical circuits can be implemented as shown in <u>Figure 12</u>. In this type of implementation, the magnetic loop surface is the same and the H-field is generated on the opposite side. This tends to cancel them out if the coupling factor is sufficient and surface area and currents are the same.

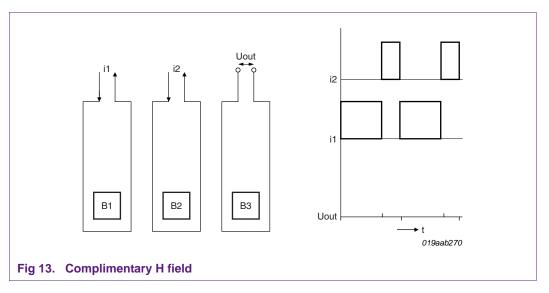

#### 5.5.2 Complementary magnetic loops

The voltage induced in a parasitic inductance is equal to the change in magnetic flux during the same period. This flux change can be limited by placing loops in close proximity (or overlapping them) where the product of surface area and current is the same. This solution can be used in several SMPS topologies.

#### **SMPS EMC and layout guidlines**

<u>Figure 13</u> displays two current loops creating magnetic fields B1 and B2. Loop B3 represents the victim line over which the potential  $U_{out}$  is generated. Because the flux change in time is close to zero, there is only voltage over  $U_{out}$  when I2 and I1 take over. The difference in coupling between B1-B3 and B2-B3 causes small spikes.

#### 5.5.3 Connecting VCC close to ground

When ground and VCC pins are close together, the magnetic coupling can be close to 0.8 and the mutual inductance can reach the self-inductance of one pin and cancel the magnetic field of the total inductance of the pins. This is true when ground current and supply current have the same magnitude and the same phase

#### 5.5.4 Increasing the PCB connection widths

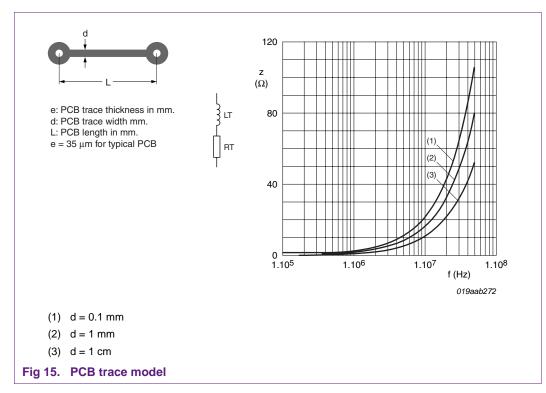

Realistically, a power-supply connection is not a pure short-circuit, but a trace with parasitic elements such as resistors and inductors.

#### **SMPS EMC and layout guidlines**

This PCB trace is a complex impedance which varies with the frequency. Figure 15 shows the plot of the impedance versus the frequency for three different trace widths that have the same length of 10 cm and thickness of 36  $\mu$ m. A PCB trace introduces voltage ripples and the width of PCB traces have to be large enough not to introduce a voltage drop which could be too high. For example, when a 0.1 A current at 30 MHz flows through a PCB trace with 10 cm length and 0.1 mm width, it causes a 0.62 V voltage drop. If the width is 1 cm (100 times the previous one), the voltage drop is reduced by a factor of two.

$$LT(\mu H) = 0.2 \times L \times \left[ Ln \left( \left( \frac{2 \times L}{d+e} \right) + 0.5 + 0.22 \times \frac{d+e}{L} \right) \right]$$

(9)

$$RT\left(m\Omega\right) = 17 \times \frac{L}{d+e} \tag{10}$$

#### 5.6 Reducing the parasitics of all devices

In addition to the magnetics fields that are a result of PCB traces, there are also a number of other parasitics such as ground impedances, capacitor serial resistances, inductor parasitic capacitances etc. There are a number of points that can improve EMC performance based on these parasitics.

#### 5.6.1 Selecting the appropriate PCB technology

There are guidelines that determine the PCB technology to be applied at certain signal frequencies. Not complying with these guidelines will limit the possibilities for EMC reduction to a level where compliance is not possible without additional measures such as external shielding and additional filters. Table 1 shows which PCB technologies are commonly applied, depending on signal speed.

#### SMPS EMC and layout guidlines

Table 1. PCB technology selection

| Board type                                                             | Digital frequency | Signal<br>rise/fall | Remarks                                         |

|------------------------------------------------------------------------|-------------------|---------------------|-------------------------------------------------|

| Single layer single-sided                                              | <5 MHz            | >6 nS               | $10 \times F_{clock} = 1/(\pi \times T_{rise})$ |

| Single layer double-sided Tracks on both sides                         | <10 MHz           | >3 nS               | realize ground grid                             |

| Single layer double-sided<br>Ground plane on one side, wire<br>jumpers | <20 Mhz           | >1.5 nS             | ground connectors/ICs                           |

| Single layer double-sided Ground plane on one side                     | <30 MHz           | >1 nS               | no long slots allowed in ground plane           |

| Multilayer                                                             | -                 | -                   | -                                               |

#### 5.6.2 Using the ground and power planes

Ground and power planes help to reduce parasitic inductance on the board thereby reducing inductive coupling. A ground or power plane will, however, increase the parasitic capacitance of tracks with high  $^{\rm dV}\!_{\rm dt}$ , such as the drain of switching MOSFETs. Ground planes will reduce the ground lifting effect. A power plane must be adequately decoupled to ground in order to have a beneficial effect on EMC. Large uncoupled power planes will act as E-field radiator thereby worsening the EMC signature.

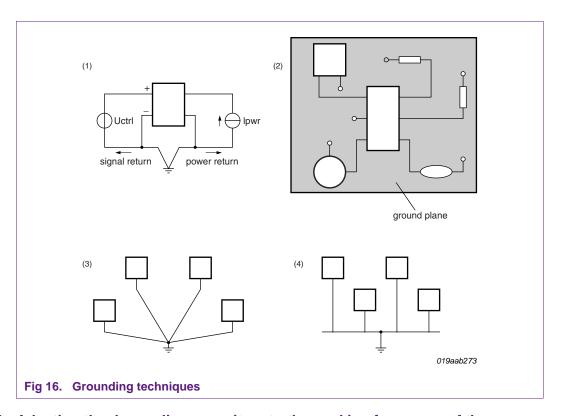

#### 5.6.3 Grounding techniques

Due to stray currents in the ground circuit, there can be unwanted build-up of potential on other sensitive locations. This is referred to as "ground lifting". To prevent ground lifting, a number of techniques can be applied, including the following:

- Do not route the signal trace return and power trace return over the same ground trace

- Separate the power ground and the signal ground [see Figure 16 (1)]

- Use the ground plane [see Figure 16 (2)]

- Apply a star configuration [see Figure 16 (3)]

- Use the ground bus [see Figure 16 (4)]

#### **SMPS EMC and layout guidlines**

## 5.6.4 Adapting the decoupling capacitors to the working frequency of the converter

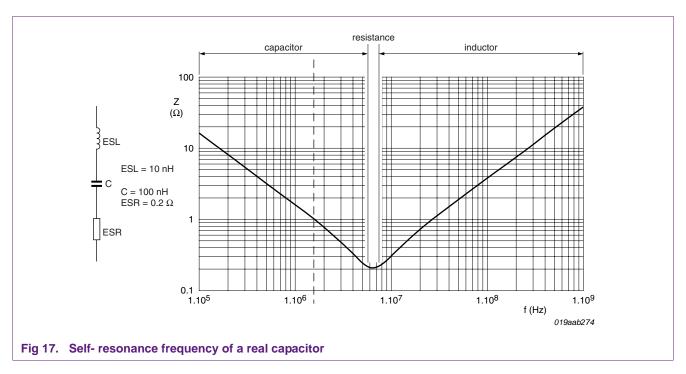

A capacitor is not pure, and can be modelled as an RLC circuit. Surface mounted devices (SMD) have the smallest internal and external inductances and this type must be selected to get the best results. Figure 17 shows the equivalent electrical model and plots the frequency response for a SMD 100 nF capacitor. The capacitor may act like a capacitor, a resistor or an inductor, depending on the frequency bands.

#### **SMPS EMC and layout guidlines**

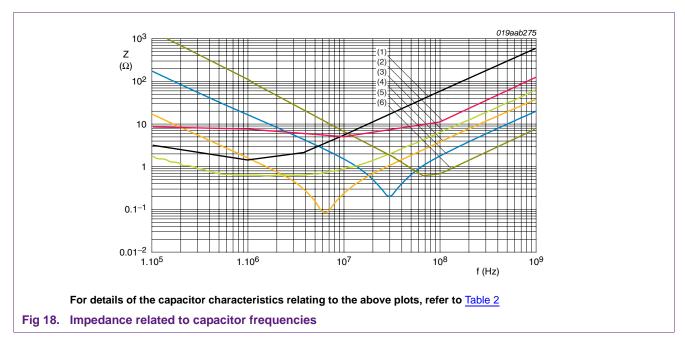

The frequency behavior depends on the type of capacitor.  $\underline{\text{Table 2}}$  gives the electrical characteristics for different capacitors.

Table 2. Capacitor characteristics

| Capacitor |        |              | Parameter |        |                    |

|-----------|--------|--------------|-----------|--------|--------------------|

| Plot[1]   | Value  | Type         | R (Ohm)   | L (nH) | Fr (MHz)           |

| 1         | 1 μF   | electrolytic | 1.8       | 13     | 0.8[2]             |

| 2         | 10 μF  | electrolytic | 6.4       | 49     | 10[2]              |

| 3         | 1μF    | tantalum     | 0.8       | 6      | 2 <mark>[2]</mark> |

| 4         | 100 nF | ceramic      | 0.08      | 3      | 7.1                |

| 5         | 10 nF  | ceramic      | 0.2       | 3      | 29                 |

| 6         | 1 nF   | ceramic      | 0.7       | 3      | 22                 |

<sup>[1]</sup> For the capacitor plots, refer to Figure 18

Figure 18 shows the plots of the frequency response for different types of capacitors.

<sup>[2]</sup> Highly damped

#### **SMPS EMC and layout guidlines**

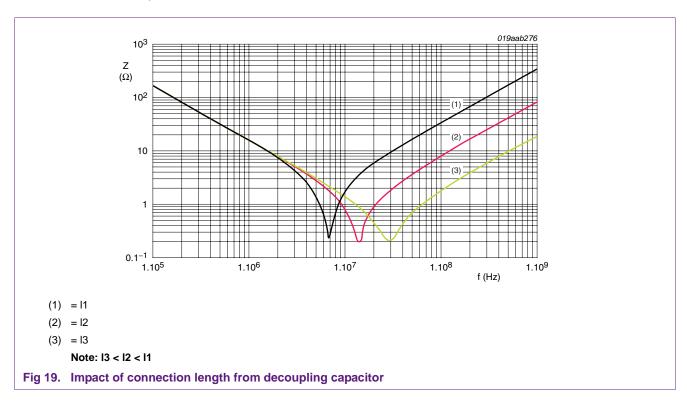

#### 5.6.5 Shortening the length of the capacitor connections

If the capacitor value is assumed to be constant, the resonance frequency depends on the inductance. The total inductance of the circuit consists of the intrinsic capacitor inductance and the inductance of the connections. A higher inductance value results in a lower resonance frequency. It is recommended to keep the length of the connections as short as possible.

SMPS EMC and layout guidlines

#### 5.6.6 Selecting suitable COG and NPO dielectric capacitor types

When selecting capacitors, the dielectric material determines ESR and subsequently the filtering function. Capacitors utilizing these dielectrics have the lowest ESR, good temperature stability and cover a wide range of values from low to high nF. Additional information relating to class I dielectrics can be found in <u>Section 7.1.1 "Class I dielectrics"</u>.

#### 5.6.7 Selecting suitable by-pass electrolytic capacitors

<u>Table 2</u> and <u>Figure 18</u> demonstrate how electrolytic capacitors tend to have an ESR that is substantially higher than ceramic capacitors. A high ESR gives the following effects:

- It lowers effective damping of a filter at high frequency

- It increases dissipation within the components, causing self-heating, higher operating temperature and decreased lifetime of the electrolytic capacitor

- It dissipates high frequency energy in the system

The first two aspects are undesirable, but the last aspect can be exploited to reduce the EMC signature. If the electrolytic capacitor is placed parallel to a ceramic capacitor, the resulting ESR will be less. Care should be taken to position the bypassing capacitor towards the noise source, because trace inductances would otherwise hamper functionality.

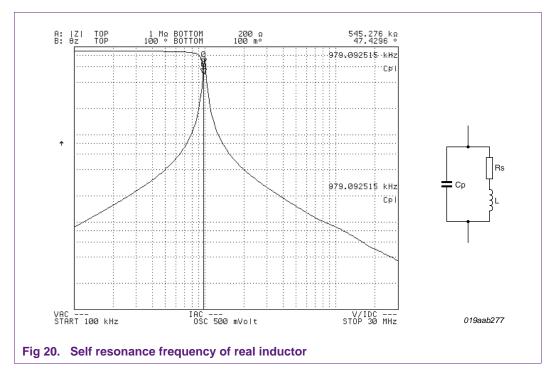

#### 5.6.8 Adapting the inductors to the working frequency of the converter

A situation similar to that mentioned in Section 5.6.4 for capacitors, is also valid for inductors. The inductor can be modeled using a series resistor Rs and a parallel capacitor Cp, resulting in a different network with an impedance curve. Figure 20 plots the inductance of a 4.7 mH Toko inductor. It has a resonance frequency at 979 kHz, a series resistor of 26  $\Omega$  and a parallel capacitance of 5.5 pF. Again, three frequency bands can be seen as follows:

- Low frequency band: 0 Hz to 980 kHz the inductor is a combination of inductance and DC resistance

- Resonance frequency: 980 kHz the inductor is an isolator (545 kΩ)

- Medium frequency: > 980 kHz the inductor acts as a pure capacitance

#### **SMPS EMC and layout guidlines**

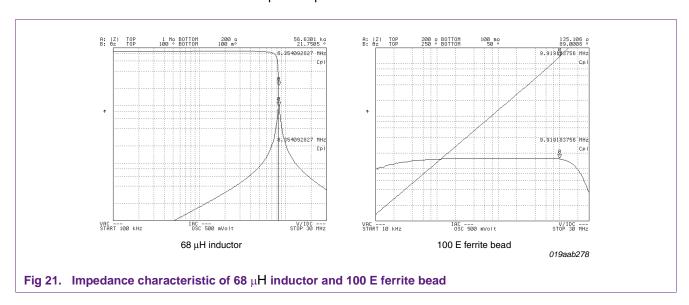

Figure 20, shows that this inductor will not be applicable at frequencies above 980 kHz. As a comparison, in Figure 21 a 68  $\mu$ H inductor and a 100 E ferrite bead are plotted. Notice that the ferrite bead displays resistive behavior that increases logarithmically with frequency. A ferrite bead has a completely different functionality compared to an inductor, it will dampen high frequency signals. The 68  $\mu$ H inductor has a self resonance frequency at 8.35 MHz and can be used to filter frequencies higher than the 4.7 mH inductor can. The ferrite bead can be used up to 30 MHz, and has little effect at low frequencies such as 10 kHz. It should be stated that the desired impedance is achieved only when the inductor is operated within the specifications. An inductor that reaches saturation looses its functionality and will not posses its original value at all. This situation often happens with inrush currents or repetitive peak currents.

AN10912

#### SMPS EMC and layout guidlines

#### 5.6.9 Prevention of mutual coupling between the inductors

Inductors and transformers have stray magnetic fields that affect the surroundings. When two inductors are placed in close proximity, the stray magnetic field of one inductor will induce a voltage over the other. This can bypass filter function.

The following three measures are employed to prevent this:

- Increase the distance between the inductors. In the near field, the H-field will decrease with  $\frac{1}{3}$  rd power of distance. Doubling the distance will reduce the induced voltage to  $\frac{1}{9}$  th.

- Set the inductor's perpendicular. If the directions of the magnetic fields do not coincide, mutual inductance is reduced.

- Use shielded inductors. Shielded inductors have less stray field

#### 5.6.10 Increase the distance

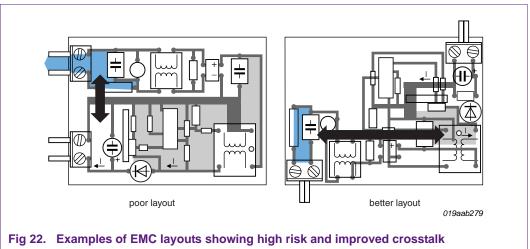

Both capacitive and inductive coupling are influenced by the distance between source and victim. Increasing the distance will reduce the risk of the unwanted bypassing of filter networks or crosstalk. See Figure 22

configurations

#### 5.7 Frequency domain analysis

When EMC problems are analyzed, it is often possible to find a link between the problems and the solution by looking at the frequency band. If a converter operates at 100 kHz, harmonics will occur at 200 kHz, 300 kHz etc. A signal at 5 MHz will not be caused by the converter harmonics, but more likely as the result of ringing or steep switching flanks.

#### SMPS EMC and layout guidlines

#### 5.7.1 Differential and common mode noise

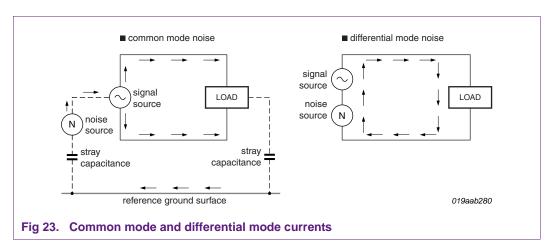

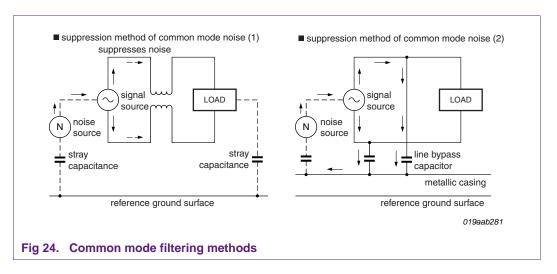

For conducted emission, two modes are classified:

- Differential mode noise is conducted on the signal (L) line and neutral (N) line in the

opposite direction to each other. This type of noise is suppressed by installing a filter

on the hot (VCC) side on the signal line or power supply line, as mentioned in the

preceding chapter

- Common mode noise appears equally (with respect to local circuit common) on both lines of a 2-wire cable not connected to earth, shield, or local common. Common mode noise can be suppressed either by using a coupled inductor in the signal path over both lines, or by using shielding with capacitive grounding

Figure 23 and Figure 24 show the resultant signals.

During EMI testing, it is possible to detect whether there is common mode or differential mode noise. With this information, the appropriate countermeasures can be taken.

#### SMPS EMC and layout guidlines

As common mode noise can be caused by stray capacitance to ground, it can be seen as frequency dependent. The reactance of a capacitor is calculated using <u>Equation 11</u>.

$$X_c = \frac{1}{-j \times \omega \times C} \tag{11}$$

Where  $\omega = 2 \times \pi \times f$ .

If the impedance is estimated to be equal to 100  $\Omega$  (line impedance), and the stray capacitance at 10 pF, the cut-off frequency is calculated using Equation 12.

$$f = \frac{1}{2 \times \pi \times 100 \times 10E - 12} = 159 \text{ MHz}$$

(12)

This is obviously a high frequency phenomenon. However, low frequency conducted emission is more likely differential mode by nature, and can best be filtered with a differential mode filter such as a symmetrical  $\pi$  filter.

#### 5.7.2 X and Y type capacitors

A line-to-line capacitor (designated as type X) properly applied is effective for differential mode filtering. A line to ground capacitor (type Y) provides filtering for common mode noise. While X capacitor may be of any practical value, Y capacitors generally need to be kept to small values to limit the 50 Hz to 60 Hz leakage current to ground. A typical value for a Y capacitor is 4700 pF. Common X capacitor values are from 0.1  $\mu F$  up to1.0  $\mu F$ . Sometimes even higher values are required depending on the interference frequencies. Improved printed-circuit layout practices will result in smaller capacitor values being required. Also, two X capacitors of smaller value are generally better, especially in the  $\pi$ -configuration with a choke.

Due to their placement on the AC line, a failed RFI suppression capacitor is capable of causing injury either by shock or fire. The problem is exacerbated by conditions on the line. The line conducts voltage surges and transients on a daily basis and these often attain amplitudes of several kilovolts. Because of the potential for injury the various safety agencies provide testing and recognition for X and Y capacitors. The European standard for RFI capacitors (IEC384-14) is EN132400. The USA standard is UL1414.

#### 5.7.3 Damping any unwanted HF signals

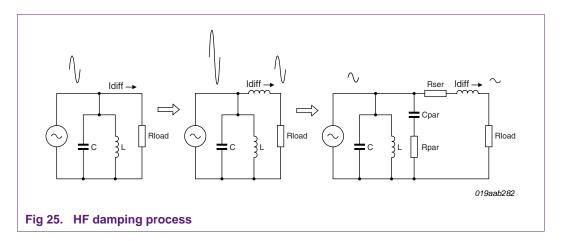

HF noise is often caused by resonance of a particular circuit. This resonance is typical for an LC combination without load. Because there is a short wavelength and steep dV/dt, these signals are much more prone to parasitic coupling and radiation to the surroundings. Filtering will increase impedance of the resonant circuit. This will in turn increase the amplitude of the resonance and increase leakage into parasitics. As a result, the noise will find another way to leak. It is therefore necessary to damp these signals. This can be achieved by either using parallel damping with a resistor and capacitor in series, serial damping using a ferrite bead, or a combination of the two. The combination of filtering and damping will isolate the signal and provide better power transfer to the damping element. Figure 25 shows this process.

#### SMPS EMC and layout guidlines

#### 5.8 Shielding

#### 5.8.1 Mount the hot windings at the inner layer

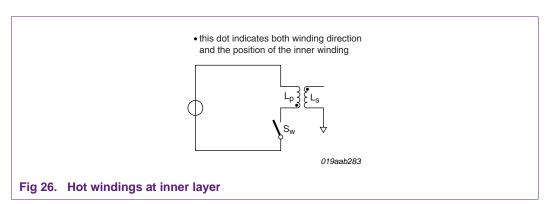

The outer windings of inductors and transformers can act as a shield when connected to a stable potential. This is capacitive shielding as the area having most dV/dt is covered by conductive material. Although the dot shown in <a href="Figure 26">Figure 26</a> only indicates current flow and winding direction, it is also often interpreted as the location of the first winding (see <a href="Figure 26">Figure 26</a>).

#### 5.8.2 Attach a heatsink to the clean potential

Heat-sinks distribute heat away from dissipative elements. In SMPS systems, these dissipative element are usually the components that carry high currents and voltages, switches for example. Because of the close proximity of the heat-sinks to these devices, capacitive coupling always occurs. This results in the complete heat-sink becoming a capacitive radiator to its surroundings. This is particularly evident where common mode noise is present. It is therefore recommended that heat-sinks are connected either directly to a clean potential, such as a clean ground signal, or the use of a decoupling capacitor to conduct noise toward a clean potential.

#### 5.8.3 Use the component material and heatsink as a shield

Some components, including grounded heat-sinks, can act as shielding for capacitive conducted noise. One of the constructional methods often encountered in power supplies, is the use of a heatsink to disperse heat, act as shield and also to provide a mechanical housing. Because the functionality is combined, it is an economical solution. Another

#### SMPS EMC and layout guidlines

option would be to use components, such as decoupling capacitors, in such a way that they are positioned between the noise source and the victim. The internal conductive material acts as a shield again. The outer area of the component must be connected to a clean potential.

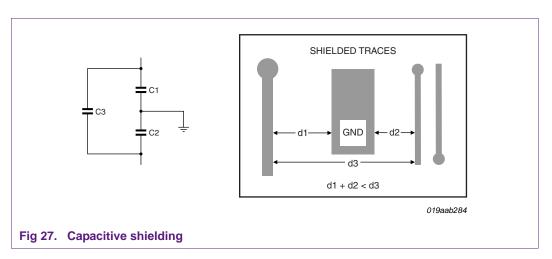

#### 5.8.4 Using capacitive shielding

To reduce parasitic coupling to susceptible lines, capacitive shielding can be implemented by putting a trace with fixed potential between the lines. A fixed clean potential, such as a ground, is essential for this. Conductive material that is not connected, gives a larger resultant capacitance and therefore more parasitic coupling, which will make the problem worse.

#### 5.8.5 De-couple other floating potentials

It is usual to de-couple other floating potentials, such as a metal housing, towards a clean fixed potential, such as the mains neutral or safety earth. This avoids capacitive coupling towards the surroundings that will generate a common mode noise conductive path. If this decoupling is done over a safety barrier, (isolation between mains and a low voltage secondary side of the SMPS), the decoupling capacitor should be selected to withstand the required voltage. Type Y capacitors have been approved for this purpose. Care should be taken that 50 Hz to 60 Hz leakage current to ground is not exceeded, by combining multiple type Y capacitors.

#### 6. Conclusion

Most of the EMC improvements detailed in this application note are already known but not always applied. There is not one specific solution for improving the EMC of a system, but a number of individual precautions contribute to a cumulative improvement. Designers must keep in mind these mechanisms, and apply them early in the conceptual phase of a system to ensure EMC compliance. The more that these considerations and countermeasures are used during early design stages, the more that cost and effort will be reduced and delays prevented during more final development stages.

**SMPS EMC and layout guidlines**

#### 7. Additional information

#### 7.1 Industry ceramic capacitor markings

#### 7.1.1 Class I dielectrics

The electronics industry has defined several classes of ceramic dielectric capacitors. Class I ceramics have dielectric constants below 150, and are the most stable ceramic capacitors. The basic ceramic is the para-electric oxide TiO2. By adding small amounts of ferro-electric oxides such as CaTiO3 or SrTiO, extended temperature compensating ceramics are created.

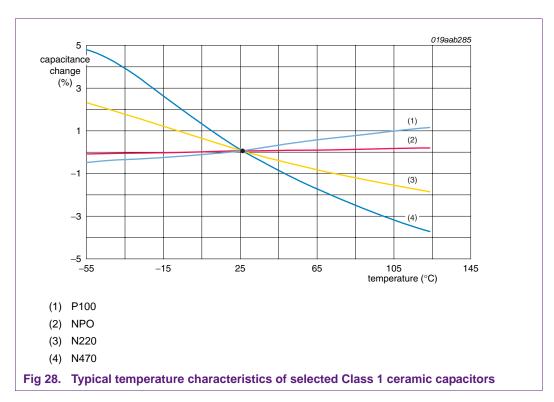

These ceramics have linear and predictable temperature characteristics and dielectric constants up to approximately 500. Class I dielectric capacitors have typical tolerances of 5 % and values within the range 4.7 pF to 0.047  $\mu$ F. Their capacitance is highly stable over time, and they have a small dissipation factor over a wide range of frequencies. Figure 28 shows the typical variation in capacitance for a selection of Class 1 ceramic capacitors.

The variation in capacitance with temperature is clearly not perfectly linear, but close enough so that a linear approximation is reasonable and a temperature coefficient can be defined.

The unofficial, colloquial temperature coefficient designations for the capacitors are indicated in <u>Figure 28</u>. The temperature coefficient is given as "P" for positive, "N", for negative, followed by a 3-digit value of the temperature coefficient in ppm/°C. For example "N220", is -200 ppm/°C, and "P100" is +100 ppm/°C. The one exception to this system is "NPO" (where an "O" instead of "0" is used) which means stable with temperature.

#### **SMPS EMC and layout guidlines**

#### 7.1.2 EIA capacitor codes

The EIA three character code, for the material capacitance/temperature slope, is derived from the high and low temperature limits, and the range of capacitance change.

Table 3. EIA codes

| ppm/°C | Multiplier | Tolerance in ppm/°C (25°C to 85°C) |

|--------|------------|------------------------------------|

| C: 0.0 | 0: –1      | G: ±30                             |

| B: 0.3 | 1: –10     | H: ±60                             |

| L: 0.8 | 2: -100    | J: ±120                            |

| A: 0.9 | 3: -1000   | K: ±250                            |

| M: 1.0 | 4: +1      | L: ±500                            |

| P: 1.5 | 6: +10     | M: ±1000                           |

| R: 2.2 | 7: +100    | N: ±2500                           |

| S: 3.3 | 8: +1000   |                                    |

| T: 4.7 |            |                                    |

| V: 5.6 |            |                                    |

| U: 7.5 |            |                                    |

#### 7.1.3 dB and mV

During EMC measurements, the interference level is often expressed in  $dB\mu V$ . The relation is expressed in Equation 13. Equation 14 and Equation 15

$$U(dB\mu V) = 20 \times {}^{10}log U(\mu V) \tag{13}$$

$$120 (dB\mu V) = 10^6 \mu V = 1 V \tag{14}$$

$$U\left(\mu V\right) = 10^{\frac{dB\mu V}{20}} \tag{15}$$

The advantages of this are as follows:

- · Small numbers with many orders of magnitudes

- Divisions become subtractions

- Multiplications become additions

#### SMPS EMC and layout guidlines

#### 8. Abbreviations

Table 4. Abbreviations

| Acronym | Description                  |

|---------|------------------------------|

| PCB     | Printed-Circuit Board        |

| ESR     | Equivalent Series Resistor   |

| HF      | High Frequency               |

| AC      | Alternating Current          |

| RFI     | Radio Frequency Interference |

| SMD     | Surface Mounted Device       |

#### 9. Glossary

**SMPS** — Switch Mode Power Supply

**EMC** — ElectroMagnetic Compatibility: the ability of a product to coexist in its intended electromagnetic environment without causing or suffering functional degradation or damage.

**EMI** — ElectroMagnetic Interference: a process by which disruptive electromagnetic energy is transmitted from one electronic device to another via radiated or conducted paths (or both).

Radiated emission — Energy transmitted by the air via antenna or loops.

**Conducted emission** — Energy transmitted via solid medium cables, PCB connections, packages etc.

**Noise source** — A source that generates an electromagnetic perturbation.

**Victim** — An electronic device that receives a perturbation which causes dysfunction.

**Coupling path** — A medium that transmits energy from the noise source to the victim.

**COG** — EIA three character code for the material capacitance-temperature slope.

**NPO** — Industry code for capacitor material with lowest temperature coefficient.

#### SMPS EMC and layout guidlines

#### 10. References

- [1] IEC 61000-1 Introduction, terms, and conditions

- [2] IEC 61000-2 Classification of electromagnetic environments

- [3] IEC 61000-3 Limits and disturbance levels.

- [4] IEC 61000-4 Testing and measurement techniques

- [5] IEC 61000-5 Installation and mitigation guidelines

- [6] IEC 61000-6 Generic standards

- [7] CISPR 11/EN 55011 Emission standard for industrial, scientific, and medical (ISM) radio RF equipment (see Figure 23).

- [8] CISPR 13/EN 55013 Emission standard for broadcasting equipment such as radio, television, etc.

- [9] CISPR 14/EN 55014 Emission standard for household apparatus and portable tools

- [10] CISPR 15/EN 55015 Emission standards for luminaires

- [11] CISPR 20/EN 55020 Immunity standard for broadcasting equipment, such as radio and television

- [12] CISPR 22/EN 55022 Emission standard for information technology equipment (ITE).

- [13] EN 55014-1, EN 55014-2 Emissions and immunity requirements for household apparatus and portable tools.

- [14] EN 55103-1, EN 55103-2 Emissions and immunity requirements for professional audio and video equipment.

- [15] IEC 555-2/EN 60555-2 LF Emissions standard concerning harmonics for household products.

- [16] IEC 555-3/EN 60555-3 LF emissions standard concerning flicker and voltage variations for household products.

- [17] IEC 61000-3-2/EN 61000-3-2 Limits for harmonic current emissions.

- [18] IEC 61000-3-3/EN 61000-3-3 Limitation of voltage changes, voltage fluctuations and flicker in public low-voltage supply systems.

#### SMPS EMC and layout guidlines

#### 11. Legal information

#### 11.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 11.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law. even if any remedy fails of its essential purpose.

Safety of high-voltage evaluation products — The non-insulated high voltages that are present when operating this product, constitute a risk of electric shock, personal injury, death and/or ignition of fire. This product is intended for evaluation purposes only. It shall be operated in a designated test area by personnel that is qualified according to local requirements and labor laws to work with non-insulated mains voltages and high-voltage circuits.

The product does not comply with IEC 60950 based national or regional safety standards. NXP Semiconductors does not accept any liability for damages incurred due to inappropriate use of this product or related to non-insulated high voltages. Any use of this product is at customer's own risk and liability. The customer shall fully indemnify and hold harmless NXP Semiconductors from any liability, damages and claims resulting from the use of the product.

#### 11.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

AN10912 **NXP Semiconductors**

#### **SMPS EMC** and layout guidlines

#### 12. Contents

| 1              | Introduction                                                                     |

|----------------|----------------------------------------------------------------------------------|

| 2              | Scope 5                                                                          |

| 3              | Topology of the EMC environment 6                                                |

| 4              | Basic checklist for EMC compliance 7                                             |

| 4.1            | Reducing the HF signature of the system 7                                        |

| 4.2            | Reducing the magnetic loops of the PCB 7                                         |

| 4.3            | Cancelling the H field                                                           |

| 4.4            | Reducing the parasitics of all devices 7                                         |

| 4.5            | Frequency domain analysis 8                                                      |

| 4.6            | Shielding 8                                                                      |

| 5              | Reducing the HF signature of the system 9                                        |

| 5.1            | Slope and duty factor control 9                                                  |

| 5.2            | Filtering and damping at the noise source 10                                     |

| 5.3            | Adapting converter frequency to an EMC                                           |

| 5.4            | curve                                                                            |

| 5.4.1          | Decreasing the surface area of the magnetic                                      |

|                | loops                                                                            |

| 5.4.2          | Magnetic loop and ohmic voltage drop 11                                          |

| 5.4.3          | Parasitic inductance                                                             |

| 5.4.4          | Preventing edge radiation                                                        |

| 5.4.5          | Microstrip topology                                                              |

| 5.4.6          | Reducing VCC/VSS network                                                         |

| 5.4.7          | Shortening the loops around the oscillator 14                                    |

| 5.5            | Cancelling the H field                                                           |

| 5.5.1          | Opposite magnetic loops                                                          |

| 5.5.2          | Complementary magnetic loops                                                     |

| 5.5.3          | Connecting VCC close to ground 16                                                |

| 5.5.4          | Increasing the PCB connection widths 16                                          |

| 5.6            | Reducing the parasitics of all devices 17                                        |

| 5.6.1          | Selecting the appropriate PCB technology 17 Using the ground and power planes 18 |

| 5.6.2          |                                                                                  |

| 5.6.3<br>5.6.4 | Grounding techniques                                                             |

| 5.6.4          | Adapting the decoupling capacitors to the working frequency of the converter 19  |

| 5.6.5          | Shortening the length of the capacitor                                           |

| 3.0.3          | connections                                                                      |

| 5.6.6          | Selecting suitable COG and NPO dielectric                                        |

| 0.0.0          | capacitor types                                                                  |

| 5.6.7          | Selecting suitable by-pass electrolytic                                          |

|                | capacitors                                                                       |

| 5.6.8          | Adapting the inductors to the working                                            |

|                | frequency of the converter                                                       |

| 5.6.9          | Prevention of mutual coupling between the                                        |

|                | inductors                                                                        |

| 5.6.10         | Increase the distance 24                                                         |

| 5.7            | Frequency domain analysis 24                                                     |

| 5.7.1 |                                           | 25 |

|-------|-------------------------------------------|----|

| 5.7.2 | X and Y type capacitors                   | 26 |

| 5.7.3 | Damping any unwanted HF signals           | 26 |

| 5.8   | Shielding                                 | 27 |

| 5.8.1 | Mount the hot windings at the inner layer | 27 |

| 5.8.2 | Attach a heatsink to the clean potential  | 27 |

| 5.8.3 | Use the component material and heatsink   |    |

|       | as a shield                               | 27 |

| 5.8.4 | Using capacitive shielding                | 28 |

| 5.8.5 | De-couple other floating potentials       | 28 |

| 6     | Conclusion                                | 28 |

| 7     | Additional information                    | 29 |

| 7.1   | Industry ceramic capacitor markings       | 29 |

| 7.1.1 | Class I dielectrics                       | 29 |

| 7.1.2 | EIA capacitor codes                       | 30 |

| 7.1.3 | dB and mV                                 | 30 |

| 8     | Abbreviations                             | 31 |

| 9     | Glossary                                  | 31 |

| 10    | References                                | 32 |

| 11    | Legal information                         | 33 |

| 11.1  | Definitions                               | 33 |

| 11.2  | Disclaimers                               | 33 |

| 11.3  |                                           | 33 |

| 12    | Contents                                  | 34 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2011. All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 18 February 2011 Document identifier: AN10912